# A 40W Dual-Inductor Hybrid Converter with Flying-Capacitor-Tapped Auxiliary Stage for Fast Transient Response in 48V PoL Automotive Applications

Nameer Khan<sup>1</sup>, Katherine Liang<sup>1</sup>, Tristan Robitaille<sup>1</sup>, Gerard Villar Piqué<sup>2</sup>,

John Pigott<sup>2</sup>, Henk Jan Bergveld<sup>2</sup>, and Olivier Trescases<sup>1</sup>

<sup>1</sup>The Edward S. Rogers Sr. Department of Electrical and Computer Engineering, University of Toronto

10 King's College Road, Toronto, ON, M5S 3G4

<sup>2</sup>NXP Semiconductors Inc.

Abstract-Advancements in autonomous vehicles have led to a proliferation of onboard electronics, frequently making use of high-performance automotive-grade processors. To satisfy the resulting stringent operating requirements, the dc-dc Power Management Unit (PMU) of the processor must maintain strict voltage regulation, which is typically achieved with large and costly decoupling capacitors. This work proposes an auxiliary-assisted 4-to-1 Dual-Inductor-Hybrid (DIH) converter for fast transient response in 48V-1V applications. The auxiliary converter operates by tapping one of the flying capacitors of the DIH converter and regulates the output voltage using a capacitor-current-based Constant-On-Time control scheme. The 4-to-1 DIH converter acts as the main stage and delivers dc power from the 48V bus by regulating the auxiliary inductor current to avoid drawing dc power through the auxiliary stage. The auxiliary capacitance requirements are relaxed by leveraging the flying capacitor of the DIH converter as an energy reservoir. In simulation, the proposed system operates with a low auxiliary capacitance of 4.7 µF, which creates a 1V deviation on the auxiliary voltage during 20A load transients. A 40W experimental prototype demonstrates the feasibility of the proposed system, achieving a peak efficiency of 93.8%. The prototype regulates the output voltage of 1 V within  $\pm 60$  mV with an output capacitor of only 650  $\mu$ F while experiencing load transients up to 12.5 A.

# I. INTRODUCTION

With advancements in autonomous vehicles, onboard electronics have come to dominate the cost of automotive systems and currently account for 40% of the total system cost [1]. Consequently, existing 12V distribution networks can no longer supply the power demands of automotive electronics, which reach up to 6 kW [2]. The resulting high transient currents have led to the adoption of 48V networks in automotive systems [3], whose market is expected to increase from 2.22 billion USD in 2019 to 21 billion USD in 2027 [4]. Highperformance automotive processors are also becoming more prevalent as the integration of onboard electronics necessitates additional processing power [5], [6]. Various 48V dc-dc Power Management Units (PMUs) have attempted to address the challenge of delivering higher power to processors using advanced hybrid Switched-Capacitor (SC) topologies [7], [8] and custom magnetics [9], [10].

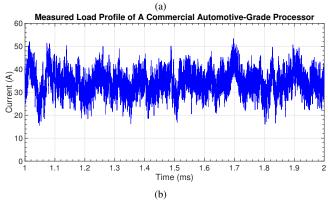

Another challenge for the dc-dc PMUs is the strict regulation of the processor core voltage (typically 0.8 V - 1.2 V) despite the highly variable load profile of the processor and the large 48V-1V conversion ratio. As an example, an autonomous-driving development platform, shown in Fig 1(a), and a measured current profile of its automotive-grade processor is shown in Fig. 1(b). Strict voltage regulation is typically achieved with a high switching frequency in the PMU and large decoupling capacitors, which degrades efficiency and leads to a large PCB footprint, respectively. For the processor shown in Fig. 1(a), a total decoupling capacitance of 5 mF is required to regulate the 1V core voltage with a tolerance of  $\pm 3\%$ .

Fig. 1: (a) Autonomous-driving development platform with an automotive-grade processor and (b) its measured load profile, with up to 12.5A load transients in 0.4 ms.

The transient response of the PMU can be improved with the use of minimum-deviation control techniques, such as Constant-On-Time (COT) [11]–[13] and current-modecontrol [14]–[16]. Minimum-deviation control schemes adjust the inductor current to the load current within one switching cycle, which minimizes the charge displaced from the output capacitor,  $C_{\rm OUT}$ , during load transients. However, the inductor-current slew rate remains constrained by the physical limit imposed by the output LC filter. Thus, further improvements in the transient response of the PMU require alternative power-processing paths.

Low-cost auxiliary converters have been used to improve the transient response of the system. By employing a lower auxiliary inductance,  $L_{AUX}$ , than the main stage inductance, the auxiliary stage alleviates the physical limit of the mainstage LC filter on the transient response of the system. To maintain a reasonable current ripple while employing a small  $L_{AUX}$ , the auxiliary stage must operate at switching frequencies much higher than the main-stage switching frequency. In [17]–[19], an auxiliary converter is connected in parallel with the main stage to supply current during load transients. Auxiliary converters have typically been presented for 12V distribution networks, but rarely for 48V PoL applications.

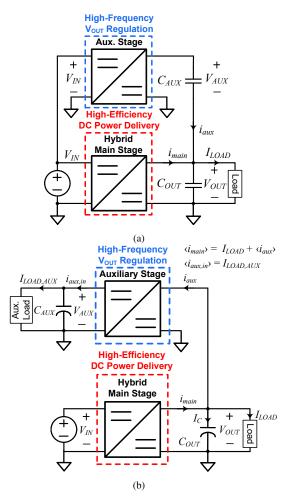

Fig. 2: Existing 48V auxiliary-assisted hybrid converters with (a) adaptive slew rate control, and (b) a  $V_{\rm IN}$ -decoupled auxiliary stage.

In [20], an ac-coupled 48V auxiliary stage with adaptive inductor-current slew rate is proposed for output-voltage regulation, as shown in Fig. 2(a). An ac-coupled capacitor is inserted in series with the auxiliary inductor. Adjusting the voltage of this capacitor enables control of the inductor slew rate. However, the auxiliary stage operates directly from the 48V bus, which causes substantial losses due to the highfrequency operation. Due to the voltage derating of capacitors, maintaining the nominal value of the ac-coupled capacitor can be costly as well, when operating with high bias voltages (e.g.,  $V_{\rm IN}/2$ ). In [21], an auxiliary stage regulates the output voltage using a buffer capacitor,  $C_{AUX}$ , that is decoupled from the input voltage, V<sub>IN</sub>, as shown in Fig. 2(b). The 48V main hybrid stage regulates the buffer capacitor voltage,  $V_{AUX}$ , to ensure that the input voltage of the auxiliary stage does not collapse. Since the auxiliary stage does not interact directly with the high  $V_{\rm IN}$  voltage, it can be optimized for switching losses with the use of low-voltage devices that have better  $R_{\rm ON} \cdot Q_G$  Figure of Merit (FoM). However, a relatively large buffer capacitance is required to ensure that the deviation on  $V_{\rm AUX}$  is constrained according to

$$\Delta V_{\rm AUX} = \int_{t_0}^{t_0 + T_{\rm SW,MAIN}} \frac{\Delta I_{\rm LOAD} \cdot V_{\rm OUT}(t)}{C_{\rm AUX} \cdot V_{\rm AUX}(t)} dt \qquad (1)$$

where  $\Delta I_{\text{LOAD}}$  is the difference between  $I_{\text{MAIN}}$  and  $I_{\text{LOAD}}$ ,  $T_{\text{SW,MAIN}}$  is the switching period of the main stage, and  $t_0$  is the time at which the load step occurs.

Fig. 3: Proposed hybrid 48V PoL converter with a flying-capacitortapped auxiliary stage.

The possibilities for an auxiliary stage are strongly dependent on the choice of the main-stage topology. Hybrid SC converters are becoming popular as the main stage topology in 48V PoL applications due to the large energy density of capacitors. However, the energy stored in the flying capacitors is poorly utilized and is mainly used to step down the input voltage by a factor of N, the native conversion ratio of the hybrid converter. To leverage this underutilized element and address the challenges presented in [20], [21], an auxiliary converter that operates by tapping the flying capacitor of a 4-to-1 Dual-Inductor Hybrid (DIH) converter as an energy source is presented in this work, as shown in Fig. 3. One of the three flying capacitors acts as an energy reservoir for the auxiliary stage to supply or sink current during load transients to reduce output-capacitance requirements. By tapping the flying capacitor with the lowest voltage, the auxiliary stage also leverages the native conversion ratio of the DIH converter to utilize better-FOM devices for low switching losses.

This paper is organized as follows. The system architecture is presented in Section II, followed by closed-loop simulation results in Section III. Experimental results from the hardware prototype are presented in Section IV, and finally, conclusions are presented in Section V.

#### **II. SYSTEM ARCHITECTURE**

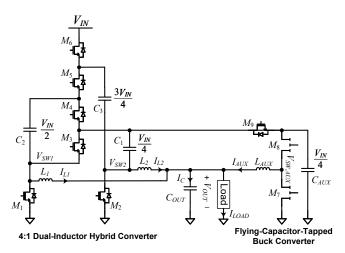

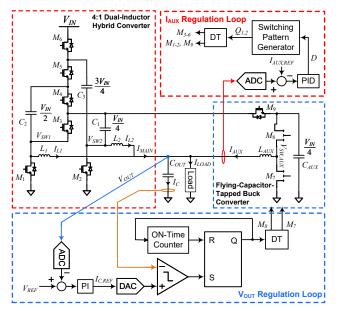

The proposed architecture, consisting of the DIH main stage and buck auxiliary stage, is shown in Fig. 4. The 4-to-1 Dual-Inductor Hybrid (DIH) converter is selected for the main stage due to its high native conversion ratio and high output-current capability [22]. A balancing controller is typically needed for the flying capacitor voltages of a hybrid switched-capacitor converter to ensure that the device blocking voltages are not exceeded. However, the DIH topology has inherent inductor current and capacitor balancing, which eliminates the need for a current-sharing controller. The flying-capacitor voltages remain balanced whilst still powering the auxiliary stage, so long as the average value of  $I_{AUX}$  remains zero. In steadystate operation, the flying capacitor only provides the auxiliary losses, which are quite small and easily replenished by the normal operation of the DIH stage. Although  $I_{AUX,ref}$  can be set to a non-zero value to leverage the auxiliary stage to deliver a portion of the load power, this creates an imbalance in the inductor currents,  $I_{L1,2}$ , such that  $I_{L1} - I_{L2} = I_{AUX}$ .

Fig. 4: Control architecture of flying-capacitor-tapped auxiliary stage.

This imbalance can be corrected by compensating the duty cycles of each DIH state, at the expense of unbalancing the flying-capacitor voltages.

The system parameters are presented in Table I. A native DIH conversion ratio of 4 was selected to provide a nominal 12V input voltage for the auxiliary stage, which enables the use of lower-voltage devices with better FoM while still providing sufficient ramp-up capability for  $I_{AUX}$ . Since the system has a low output voltage of 1 V, the falling inductor-current slew rate limits the transient performance during step-down load transients. A Constant-On-Time (COT) control scheme based on sensing the output-capacitor current, as shown in Fig. 4, is selected for the auxiliary stage to achieve minimum-deviation response during step-down load transients and maximize the transient performance for a given auxiliary inductance, LAUX. Since LAUX is constrained as it creates an inductive divider with the ESL of the output capacitor, which results in large inductive spikes on  $V_{OUT}$ , it is imperative to minimize  $L_{AUX}$ . The COT control loop regulates  $V_{\rm OUT}$  by adjusting  $I_{\rm AUX}$  to  $\Delta I_{

m LOAD}$  during transients. By setting  $T_{ON,AUX} = 60 \text{ ns}$ , the auxiliary stage operates at a high switching frequency of almost 1.4 MHz for the nominal auxiliary conversion ratio of 12V-to-1V. By maintaining an auxiliary switching frequency that is  $10 \times$  higher than  $f_{SW,DIH}$ , the auxiliary stage can reject most disturbances the main DIH stage imposes on the output node. The DIH main stage in turn regulates  $I_{AUX}$  over longer periods using an Average-Current-Mode-Control (ACMC) scheme, shown in Fig. 4, to maintain the average value of  $I_{AUX}$  at zero and avoid any steady-state imbalances in  $I_{L1,2}$ .

TABLE I: Key System Parameters

| Parameter                                        | Value   | Unit |

|--------------------------------------------------|---------|------|

| Input voltage, V <sub>IN</sub>                   | 24 - 54 | V    |

| Output voltage, $V_{OUT}$                        | 1       | V    |

| Rated Load Power, PRATED                         | 40      | W    |

| Max. Load Current Step, $\Delta I_{\text{LOAD}}$ | 20      | A    |

| Output Capacitor, C <sub>OUT</sub>               | 650     | μF   |

| DIH Switching Frequency, $f_{SW,DIH}$            | 150     | kHz  |

| DIH Native Conversion Ratio, N                   | 4       |      |

| DIH Inductors, $L_{1,2}$                         | 1.5     | μH   |

| DIH Flying Capacitors, $C_{1,2,3}$               | 10      | μF   |

| AUX On-Time, T <sub>ON,AUX</sub>                 | 60      | ns   |

| AUX Inductor, $L_{AUX}$                          | 0.12    | μH   |

| AUX Capacitor, $C_{AUX}$                         | 4.7     | μF   |

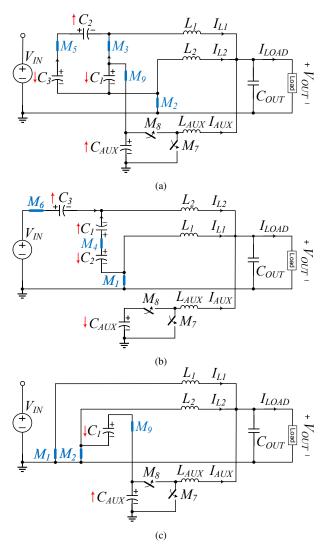

The switching states of the DIH converter are presented in Fig. 5. Since  $C_1$  is not ground-referenced in State II, the flying capacitor cannot be directly connected to the auxiliary stage. To address this issue, an additional charge-transfer switch,  $M_9$ , is used to connect  $C_1$  to the auxiliary stage. By synchronizing  $M_9$  to  $M_2$ , the relatively large on-time of the DIH low-side switches, due to the high step-down ratio, enables  $C_1$  to supply the auxiliary losses for the majority of the DIH switching cycle. Nonetheless, the auxiliary capacitance,  $C_{AUX}$ , must be sized to ensure that  $V_{AUX}$  does not collapse during load transients. When load transients occur, the auxiliary stage responds first such that  $I_{AUX} = \Delta I_{LOAD}$ , thanks to its fast control loop. While the main-stage control loop adjusts its operation to bring  $I_{AUX}$  back to zero, the auxiliary stage must supply  $\Delta I_{LOAD}$  for at least  $T_{SW,DIH}$  seconds. The majority of this current is drawn from both  $C_{AUX}$  and  $C_1$ , which greatly reduces the auxiliary capacitance requirements, as  $C_1$ replenishes  $C_{AUX}$  for the majority of the DIH switching cycle.

Fig. 5: DIH converter switching states: (a) State I, (b) State II, and (c) State 0.

With the auxiliary stage operating with a COT control scheme, the charge drawn from  $C_{AUX}$  in one auxiliary switching cycle can be approximated as

$$Q_{\rm AUX,i} = \Delta I_{\rm LOAD} \cdot T_{\rm ON,AUX} \tag{2}$$

For a given  $C_{AUX}$ , the drop in  $V_{AUX}$  in one switching cycle can be approximated as

$$\Delta V_{\rm AUX,i} = \frac{Q_{\rm AUX,i}}{C_{\rm AUX} + C_1} \tag{3}$$

Therefore, the total  $\Delta V_{\rm AUX}$  imposed during a load transient is

$$\Delta V_{\rm AUX} = \frac{k \cdot \Delta I_{\rm LOAD} \cdot T_{\rm ON,AUX}}{C_{\rm AUX} + C_1},\tag{4}$$

where k is the ratio of the DIH switching period to the auxiliary switching period and is calculated as follows

$$k = \frac{T_{\rm SW,DIH} \cdot V_{\rm OUT}}{T_{\rm ON,AUX} \cdot \frac{V_{\rm IN}}{N}},\tag{5}$$

where  $T_{\rm SW,MAIN}$  is the switching period of the DIH converter. By substituting (5) into (4), the deviation on  $V_{\rm AUX}$  for a given  $C_{\rm AUX}$  can be determined according to the following equation

$$\Delta V_{\rm AUX} = \frac{V_{\rm OUT} \cdot \Delta I_{\rm LOAD} \cdot T_{\rm SW,DIH}}{\frac{V_{\rm IN}}{N} \cdot (C_{\rm AUX} + C_1)}.$$

(6)

Based on the parameters from Table I, the deviation on  $V_{\rm AUX}$  is 0.75 V, approximately a 6% deviation from  $V_{\rm C1}$ , for  $\Delta I_{\rm LOAD} = 20$  A,  $C_{\rm AUX} = 4.7 \,\mu\text{F}$ ,  $C_1 = 10 \,\mu\text{F}$ , and a nominal conversion ratio of 48V-to-1V.

#### **III. SIMULATION RESULTS**

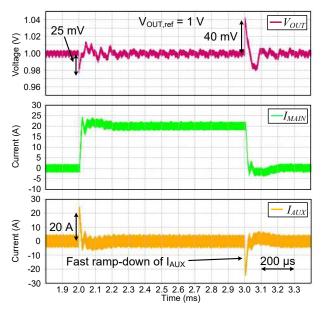

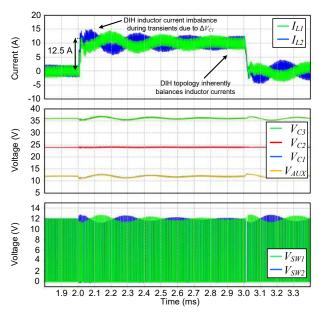

The proposed system was validated via a simulation in PLECS, with the parameters shown in Table I. Load steps of 20A were applied to the system to evaluate its transient response. The capacitor-current-based COT control scheme responds to the change in  $V_{\rm OUT}$  and rapidly changes  $I_{\rm AUX}$ to  $\Delta I_{\rm LOAD}$ , as shown in Fig. 6. The auxiliary stage continues to provide this current until the change in  $I_{\rm AUX}$  is detected by the main DIH stage, which adjusts its inductor currents,  $I_{\rm L1,2}$  until the average value of  $I_{\rm AUX}$  returns to zero. Since the auxiliary stage supplies and sinks charge from  $C_1$ , its voltage,  $V_{\rm C1}$ , deviates from its nominal value of  $V_{\rm IN}/4$  during load transients, as shown in Fig. 7, the impact of which is

Fig. 6: Simulated output voltage deviation during 20A load steps with  $V_{\rm IN}$  = 48 V.

observed in the DIH inductor currents,  $I_{L1,2}$ . As the lower  $V_{C1}$  is applied asymmetrically to each DIH inductor, the DIH inductor currents deviate during transients. However, since the DIH converter has inherent inductor-current and capacitor-voltage balancing, the deviating quantities converge to their nominal values over time.

An output voltage deviation of 40 mV is observed during the load step-down transient with only 650 µF of output capacitance. With the proposed control scheme, the main stage detects the change in  $I_{AUX}$  and adjusts  $I_{MAIN}$  to  $I_{LOAD}$ within  $0.1 \,\mathrm{ms}$ . Since  $C_1$  provides most of the charge for the auxiliary stage,  $C_{AUX}$  is sized relatively small at 4.7 µF, which leads to a deviation of 1 V on  $V_{\text{C1}}$  as shown in Fig. 7. Due to the high conversion ratio of 48 V-to-1 V,  $C_1$  is groundreferenced for the majority of the DIH switching cycle, which minimizes the voltage deviation between  $V_{AUX}$  and  $V_{C1}$ . The DIH inductor currents,  $I_{L1,2}$ , deviate from their nominal value by up to 7.5 Å due to the variation in  $V_{C1}$ , as shown in Fig. 7. Since the DIH converter has inherent inductor-current and capacitor-voltage balancing, this imbalance is automatically corrected to restore uniform current sharing within approximately 1 ms.

Fig. 7: Simulated DIH inductor current balance due to flyingcapacitor voltage deviation during 20A load steps with  $V_{IN}$  = 48 V.

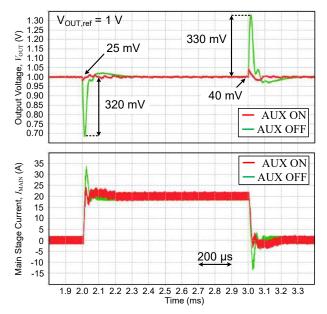

To characterize the impact of the auxiliary stage on the transient performance of the system, load transients were applied with the auxiliary stage enabled and disabled, as shown in Fig. 8. When the auxiliary stage is disabled, the main stage directly regulates  $V_{\rm OUT}$  using a well-tuned PID controller. For  $C_{\rm OUT} = 650 \,\mu\text{F}$ , this results in an overshoot of  $330 \,\text{mV}$ , while the operation of the auxiliary stage limits the overshoot to no more than  $40 \,\text{mV}$ , an  $8.25 \times$  reduction. As the main-stage inductor current is slew rate limited, its transient performance can be improved only with additional phases.

Fig. 8: Simulated load-transient response of the proposed system with the auxiliary stage enabled and disabled.

### **IV. EXPERIMENTAL RESULTS**

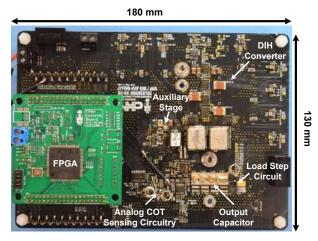

To demonstrate the feasibility of the proposed system, a 40W experimental prototype was built, as shown in Fig. 9. To optimize switching losses, 40V GaNFETs were selected for the auxiliary stage and operated at  $f_{SW,AUX} = 1.4$  MHz. Although it is advantageous for output regulation to maximize  $f_{SW,AUX}$ , it is constrained by the low on-time needed for 12V-1V conversion at high frequencies. On the other hand, the DIH switches,  $M_{1-6}$ , as well as the charge-transfer switch,  $M_9$ , were implemented with low  $R_{ds,on}$  Si MOSFETs to optimize for conduction losses, since they are operated at a much lower frequency.

Fig. 9: Experimental prototype of the auxiliary-assisted converter.

The high-speed analog sensing for the capacitor-currentbased COT control scheme was implemented on the main power-stage PCB, while the digital ACMC controller was implemented on the FPGA control board. A high-speed loadtransient circuit was also included on the main PCB to generate high-di/dt load steps. The capacitor current was measured using low-ESL current-sensing resistors to ensure that the Power Delivery Network (PDN) was not compromised. To prevent inductive parasitic spikes on  $V_{AUX}$ , the charge-transfer switch,  $M_9$  was placed on the backside of the PCB close to  $C_1$ , reducing the size of the switching node, while  $C_{AUX}$  was placed next to the auxiliary power stage.

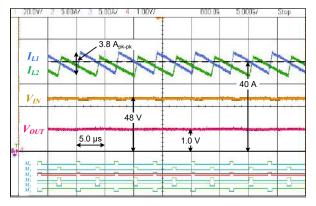

Fig. 10: Measured open-loop steady-state waveforms of the auxiliaryassisted DIH converter.

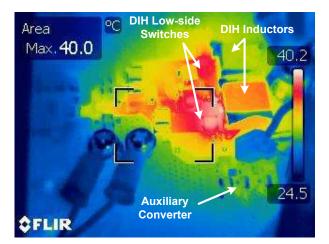

The open-loop DIH operating waveforms at an output current of 40 A are shown in Fig. 10. The mismatch in the DIH inductor currents of 0.2 A is due to the non-zero  $I_{AUX}$ , which was unregulated in this test. A thermal image of the converter at rated load and 48V-1V conversion is shown in Fig. 11. The image highlights that the low-side switches of the DIH converter,  $M_{1,2}$ , are the main source of losses in the system since they conduct the DIH inductor currents for most of the switching period. A peak temperature of 40.2°C is observed on  $M_{1,2}$ , indicating relatively low losses.

Fig. 11: Thermal image of prototype at  $I_{\text{LOAD}}$  40 A and 48V-to-1V direct conversion with forced-air cooling.

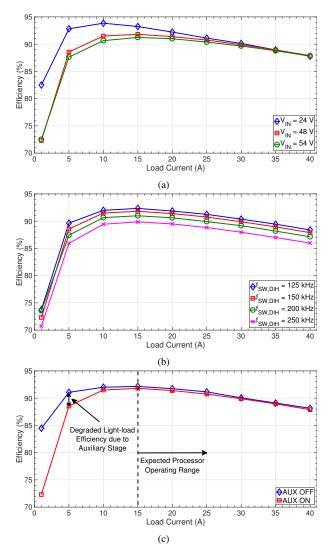

The measured system efficiency at  $V_{OUT} = 1 V$  for varying  $V_{IN}$  is shown in Fig. 12(a). Due to the lower  $V_{C1}$  at

$V_{\rm IN} = 24$  V, the auxiliary-stage losses are reduced, which leads to a 4% increase in light-load efficiency at  $I_{\rm LOAD} = 5$  A. A peak efficiency of 93.8% was achieved at  $I_{\rm LOAD} = 10$  A and  $V_{\rm IN} = 24$  V. At the nominal conversion ratio of 48 V-to-1 V, an efficiency of 87.9% was achieved at the rated load of 40 A.

By regulating  $V_{\rm OUT}$  with the auxiliary stage,  $f_{\rm SW,DIH}$  is relaxed to reduce the main-stage switching losses, as shown in Fig. 12(b). By reducing  $f_{\rm SW,DIH}$  from 250 kHz to 150 kHz, the efficiency at the rated load is improved by almost 2%. However, a lower  $f_{\rm SW,DIH}$  translates to longer settling times for the  $I_{\rm AUX}$  loop. As such, the expected frequency of load transients dictates the minimum limit for the DIH switching frequency.

Fig. 12: Measured system efficiency versus  $I_{\text{LOAD}}$  at  $V_{\text{OUT}} = 1 \text{ V}$  for (a) varying  $V_{\text{IN}}$ , (b) varying  $f_{\text{SW,DIH}}$ , and (c) with the auxiliary stage enabled and disabled.

The auxiliary losses significantly impact the light-load efficiency of the converter, as shown in Fig. 12(c). At  $I_{OUT} = 5$  A, a 2.6% drop in efficiency is observed when the auxiliary stage is enabled. However, based on the measurements from

TABLE II: State-of-the-Art 48V Auxiliary-Assisted Converters

|           | $V_{\rm IN}$ | $V_{\rm OUT}$ | $I_{\rm LOAD}$ | $\Delta I_{\rm LOAD}$ | $\Delta V_{\rm OUT}$ | $C_{\rm OUT}$ | $L_{\mathrm{MAIN}}$ | $L_{AUX}$ | $m_{\rm F,aux}$ | $V_{\rm AUX}$ | $C_{\mathrm{AUX}}$ |

|-----------|--------------|---------------|----------------|-----------------------|----------------------|---------------|---------------------|-----------|-----------------|---------------|--------------------|

|           | [V]          | [V]           | [A]            | [A]                   | [mV]                 | [µF]          | [µH]                | [nH]      | [A/µs]          | [V]           | [µF]               |

| This Work | 24-54        | 1             | 40             | 12.5                  | 60                   | 650           | 1.5                 | 120       | 8.33            | 12            | 4.7                |

| [20]      | 24-54        | 1             | 40             | 40                    | 40                   | 640           | 0.47                | 470       | 51              | 12-36         | 30                 |

| [21]      | 24-70        | 0.675-0.8     | 62.5           | 24                    | 60                   | 720           | 0.47                | 36        | 18.75-22.2      | 5             | 120                |

Fig. 1(b), automotive processors generally operate above 50% rated load power. For this range (20 A - 40 A), the impact of the auxiliary converter on the system efficiency is minimal.

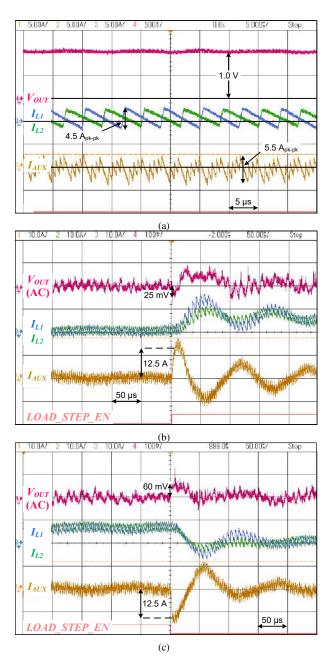

Fig. 13: Measured closed-loop waveforms: (a) steady-state, (b) load step-up, and (c) load step-down transients.

In steady-state closed-loop operation, as shown in Fig. 13(a), the  $V_{\rm OUT}$  regulation is performed by the auxiliary stage with  $I_{\rm AUX}$  varying at  $2 \cdot f_{\rm SW,DIH}$  to reject  $\Delta I_{\rm MAIN}$ . The DIH inductor currents are well-balanced since  $I_{\rm AUX}$  is regulated by the main DIH stage to have zero average value. The prototype regulates the output voltage within  $\pm 60 \,\mathrm{mV}$  during load steps of 12.5 A with only  $650 \,\mu\mathrm{F}$  of decoupling capacitance, as shown in Fig. 13(b) and 13(c). The auxiliary stage must supply the peak transient current from  $C_1$  for a duration of at least  $2 \times T_{\rm SW,DIH}$ . The deviation in  $V_{\rm C1}$  creates an imbalance in  $I_{\rm L1,2}$  during load transients that is corrected by the inherent flying-capacitor balancing of the DIH converter.

The performance of the proposed 48V auxiliary-assisted converter is compared to existing 48V auxiliary-assisted converters in Table II. While the proposed system has the lowest inductor-current slew rate,  $m_{\rm F,aux}$ , it also has the lowest auxiliary capacitance of  $4.7\,\mu\rm{F}$ , which is due to leveraging the flying capacitor of the DIH converter as an energy reservoir for the auxiliary stage.

# V. CONCLUSIONS

The proposed flying-capacitor-tapped auxiliary converter successfully achieves  $V_{OUT}$  regulation with low deviation while significantly reducing the total amount of output capacitance. The auxiliary stage leverages the existing flying capacitor in the main stage as an energy reservoir to supply current during load transients to reduce decouplingcapacitance requirements. The proposed system was simulated with the auxiliary stage enabled and disabled to highlight an  $8.25 \times$  improvement in voltage overshoot compared to the unassisted main stage. Compared to alternative 48V auxiliaryassisted converters, the auxiliary-capacitance requirements are relaxed. Since the system takes advantage of the short duty cycles of the main stage to effectively use the flying capacitor for buffering the auxiliary input, it can operate with a low auxiliary capacitance of 4.7 µF. Load transients of 12.5 A were applied to the 40W experimental prototype and an output voltage deviation of  $\pm 60 \,\mathrm{mV}$  was observed with only  $650 \,\mu\mathrm{F}$ of decoupling capacitance. A peak efficiency of 93.8% was achieved in the 40W experimental prototype, demonstrating the feasibility of utilizing the proposed topology for highperformance automotive power supplies.

## ACKNOWLEDGMENTS

This research was supported by NXP Semiconductors Inc. and The Natural Sciences and Engineering Research Council of Canada.

#### REFERENCES

- G. Chen, "Semiconductors The Next Wave." Deloitte, 2019. [Online]. Available: www2.deloitte.com/content/dam/Deloitte/tw/Documents/technologymedia-telecommunications/tw-semiconductor-report-EN.pdf

- [2] O. Sirch, J. Fröschl, M. Schäfer, "Future Vehicle Power Supply Systems with 48 Volt," in 7th International Conference Automotive 48V Power Supply Systems, 2019.

- [3] "Automotive 48V System Market (By Vehicle Class: Premium, Mid, Entry, and Luxury; By Architecture: Crankshaft Mounted, Belt Driven, Transmission Output Shaft, and Dual-Clutch Transmission-Mounted)

Global Market Size, Trends Analysis, Segment Forecasts, Regional Outlook 2020 - 2027." Precedence Research, 2020.

- [4] P. Pranav and M. Sonia, "Automotive 48V System Market." Allied Market Research, 07 2020. [Online]. Available: https://www.alliedmarketresearch.com/automotive-48vsystem-market-A06636

- [5] Intel, "New Mobileye EyeQ Ultra will Enable Consumer AVs." Intel, 2022. [Online]. Available: https://www.intel.com/content/www/us/en/newsroom/news/mobileyeces-2022-tech-news.htmlgs.jew01i

- [6] NVIDIA, NVIDIA "NVIDIA Unveils DRIVE Atlan. an Wheels AI Data Center for Next-Gen Auon Vehicles." NVIDIA, 2021. tonomous [Online]. Availhttps://nvidianews.nvidia.com/news/nvidia-unveils-nvidia-driveable: atlan-an-ai-data-center-on-wheels-fornext-gen-autonomous-vehicles

- [7] M. Choi and D.-K. Jeong, "18.6 A 92.8%-Peak-Efficiency 60A 48V-to-1V 3-Level Half-Bridge DC-DC Converter with Balanced Voltage on a Flying Capacitor," in 2020 IEEE International Solid- State Circuits Conference - (ISSCC), 2020, pp. 296–298.

- [8] R. Das, G.-S. Seo, D. Maksimovic, and H.-P. Le, "An 80-W 94.6%-Efficient Multi-Phase Multi-Inductor Hybrid Converter," in 2019 IEEE Applied Power Electronics Conference and Exposition (APEC), 2019, pp. 25–29.

- [9] Y. Chen, D. M. Giuliano, and M. Chen, "Two-Stage 48V-1V Hybrid Switched-Capacitor Point-of-Load Converter with 24V Intermediate Bus," in 2020 IEEE 21st Workshop on Control and Modeling for Power Electronics (COMPEL), 2020, pp. 1–8.

- [10] M. Ahmed, C. Fei, F. C. Lee, and Q. Li, "High-efficiency high-powerdensity 48/1V sigma converter voltage regulator module," in 2017 IEEE Applied Power Electronics Conference and Exposition (APEC), 2017, pp. 2207–2212.

- [11] S. Bari, Q. Li, and F. C. Lee, "A New Fast Adaptive On-Time Control for Transient Response Improvement in Constant On-Time Control," *IEEE Transactions on Power Electronics*, vol. 33, no. 3, pp. 2680–2689, 2018.

- [12] Li, Yu-Chen and Chen, Ching-Jan and Tsai, Chieh-Ju, "A Constant On-Time Buck Converter With Analog Time-Optimized On-Time Control,"

IEEE Transactions on Power Electronics, vol. 35, no. 4, pp. 3754–3765, 2020.

- [13] S. Tian, F. C. Lee, P. Mattavelli, K.-Y. Cheng, and Y. Yan, "Small-Signal Analysis and Optimal Design of External Ramp for Constant On-Time V<sup>2</sup> Control With Multilayer Ceramic Caps," *IEEE Transactions on Power Electronics*, vol. 29, no. 8, pp. 4450–4460, 2014.

- [14] J.-J. Chen, Y.-S. Hwang, Y. Ku, Y.-H. Li, and J.-A. Chen, "A Current-Mode-Hysteretic Buck Converter With Constant-Frequency-Controlled and New Active-Current-Sensing Techniques," *IEEE Transactions on Power Electronics*, vol. 36, no. 3, pp. 3126–3134, 2021.

- [15] K.-I. Wu, S.-H. Hung, S.-Y. Shieh, B.-T. Hwang, S.-Y. Hung, and C. C.-P. Chen, "Current-mode adaptively hysteretic control for buck converters with fast transient response and improved output regulation," in 2014 IEEE International Symposium on Circuits and Systems (ISCAS), 2014, pp. 950–953.

- [16] M.-G. Jeong, J.-G. Kang, J. Park, and C. Yoo, "A Current-Mode Hysteretic Buck Converter With Multiple-Reset RC-Based Inductor Current Sensor," *IEEE Transactions on Industrial Electronics*, vol. 66, no. 11, pp. 8445–8453, 2019.

- [17] S. Kolluri and N. L. Narasamma, "A New Isolated Auxiliary Current Pump Module for Load Transient Mitigation of Isolated/Nonisolated Step-Up/Step-Down DC–DC Converter," *IEEE Transactions on Power Electronics*, vol. 30, no. 10, pp. 5991–6000, 2015.

- [18] W. T. Ng, J. Wang, K. Ng, A. Prodić, T. Kawashima, M. Sasaki, and H. Nishio, "Digitally controlled integrated DC-DC converters with fast transient response," in 2009 IEEE International Symposium on Radio-Frequency Integration Technology (RFIT), 2009, pp. 335–338.

- [19] D. Kim, M. Hong, J. Baek, J. Lee, J. Shin, and J.-W. Shin, "Soft-Switching Auxiliary Current Control for Improving Load Transient Response of Buck Converter," *IEEE Transactions on Power Electronics*, vol. 36, no. 3, pp. 2488–2494, 2021.

- [20] N. Khan, G. Villar Piqué, J. Pigott, H. J. Bergveld, A. E. Sherif, and O. Trescases, "An Auxiliary-Assisted Dual-Inductor Hybrid DC-DC Converter with Adaptive Inductor Slew Rate for Fast Transient Response in 48-V Automotive PoL Applications," in 2022 IEEE 23rd Workshop on Control and Modeling for Power Electronics (COMPEL), 2022, pp. 1–6.

- [21] N. Khan, J. Xu, G. Villar Piqué, J. Pigott, H. J. Bergveld, A. E. Sherif, and O. Trescases, "A Wide-Input-Voltage-Range 50W Series-Capacitor Buck Converter with Ancillary Voltage Bus for Fast Transient Response in 48V PoL Applications," in 2022 24th European Conference on Power Electronics and Applications (EPE'22 ECCE Europe), 2022, pp. 1–8.

- [22] R. Das, G.-S. Seo, and H.-P. Le, "Analysis of Dual-Inductor Hybrid Converters for Extreme Conversion Ratios," *IEEE Journal of Emerging* and Selected Topics in Power Electronics, vol. 9, no. 5, pp. 5249–5260, 2021.